Intel BX80571E7500 Programming Manual - Page 52

Imt_inserts_rd, Imt_inserts_wr, Imt_ne_cycles, Imt_prealloc, Imt_valid_occupancy, Msg_addr_in_match

|

UPC - 735858206969

View all Intel BX80571E7500 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 52 highlights

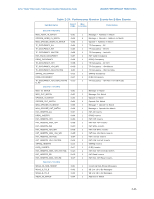

INTEL® XEON® PROCESSOR 7500 SERIES UNCORE PROGRAMMING GUIDE UNCORE PERFORMANCE MONITORING IMT_INSERTS_RD • Title: IMT Read Inserts • Category: In-Flight Memory Table • Event Code: 0x1D, Max. Inc/Cyc: 1, PERF_CTL: 1, • Definition: In-Flight Memory Table inserts of read requests (e.g. all memory read transactions targeting this B-Box as their home node and processed by this B-Box) • NOTE: Conflicts and AckConflicts are considered IMT insert events. If the conflict rate (CONFLICTS/ IMT_INSERTS_ALL * 100) is > ~5%, it is not recommended that this event (along with IMT_VALID_OCCUPANCY) be used to derive average IMT latency or latency for specific flavors of inserts. IMT_INSERTS_WR • Title: IMT Write Inserts • Category: In-Flight Memory Table • Event Code: 0x0C, Max. Inc/Cyc: 1, PERF_CTL: 1, • Definition: In-Flight Memory Table Write Request Inserts (e.g. all memory write transactions targeting this B-Box as their home node and processed by this B-Box) • NOTE: Conflicts and AckConflicts are considered IMT insert events. If the conflict rate (CONFLICTS/ IMT_INSERTS_ALL * 100) is > ~5%, it is not recommended that this event (along with IMT_VALID_OCCUPANCY) be used to derive average IMT latency or latency for specific flavors of inserts. IMT_NE_CYCLES • Title: IMT Non-Empty Cycles • Category: In-Flight Memory Table • Event Code: 0x07, Max. Inc/Cyc: 1, PERF_CTL: 2, • Definition: In-Flight Memory Table Non-Empty Cycles. IMT_PREALLOC • Title: IMT Prealloc • Category: In-Flight Memory Table • Event Code: 0x06, Max. Inc/Cyc: 1, PERF_CTL: 3, • Definition: In-Flight Memory Table in 1 DRS preallocation mode. IMT_VALID_OCCUPANCY • Title: IMT Valid Occupancy • Category: In-Flight Memory Table • Event Code: 0x07, Max. Inc/Cyc: 1, PERF_CTL: 0, • Definition: In-Flight Memory Table (tracks memory transactions that have already been sent to the memory controller connected to this B-Box) valid occupancy. Indicates occupancy of the IMT. • NOTE: A count of valid entries is accumulated every clock cycle in a subcounter. Since the IMT Queue Depth is 32, multiple this event by 32 to get a full count of valid IMT entries. MSG_ADDR_IN_MATCH • Title: Message + Address In Match • Category: Mask/Match • Event Code: 0x01, Max. Inc/Cyc: 1, PERF_CTL: 0, • Definition: Message Class and Address Match at B-Box Input. Use B_MSR_MATCH/MASK_REG MSGS_B_TO_S • Title: SB Link (B to S) Messages • Category: S-Box Interface • Event Code: 0x03, Max. Inc/Cyc: 1, PERF_CTL: 2, • Definition: Number of SB Link (B to S) Messages (multiply by 9 to get flit count). 2-40