Fujitsu MPB3043AT Product Manual - Page 69

Fujitsu MPB3043AT - Desktop 4.3 GB Hard Drive Manual

|

View all Fujitsu MPB3043AT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 69 highlights

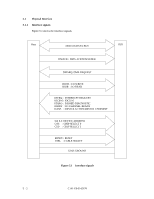

[signal] DIOR-, HDMARDY-, HSTROBE INTRQ IOCS16- CS0- CS1- DA 0-2 KEY PIDAG- DASP- [I/O] [Description] I DIOR- is the strobe signal asserted by the host to read device registers or the data port. HDMARDY- is a flow control signal for Ultra DMA data in bursts. This signal is asserted by the host to indicate to the device that the host is ready to receive Ultra DMA data in bursts. The host may negate HDMARDY- to pause an Ultra DMA data in burst. HSTROBE is the data out strobe signal from the host for an Ultra DMA data out burst. Both the rising and falling edge of HSTROBE latch the data from DATA 0-15 into the device. The host may stop generating HSTROBE edges to pause an Ultra DMA data out burst. O Interrupt signal to the host. This signal is negated in the following cases: - assertion of RESET- signal - Reset by SRST of the Device Control register - Write to the command register by the host - Read of the status register by the host - Completion of sector data transfer (without reading the Status register) When the device is not selected or interrupt is disabled O This signal indicates 16-bit data bus is addressed in PIO data transfer. This signal is an open collector output. - When IOCS16- is not asserted: 8 bit data is transferred through DATA0 to DATA7 signals. - When IOCS16- is asserted: 16 bit data is transferred through DATA0 to DATA15 signals. I Chip select signal decoded from the host address bus. This signal is used by the host to select the command block registers. I Chip select signal decoded from the host address bus. This signal is used by the host to select the control block registers. I Binary decoded address signals asserted by the host to access task file registers. - Key pin for prevention of erroneous connector insertion I/O This signal is an input mode for the master device and an output mode for the slave device in a daisy chain configuration. This signal indicates that the slave device has been completed self diagnostics. This signal is pulled up to +5 V through 10 kΩ resistor at each device. I/O This is a time-multiplexed signal that indicates that the device is active and a slave device is present. This signal is pulled up to +5 V through 10 kΩ resistor at each device. 5 - 4 C141-E045-02EN