Sharp CD-XP7700 Service Manual - Page 49

IC3 VHiLC78683E-1: MP3 Decoder LC78683E 1/2

|

View all Sharp CD-XP7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 49 highlights

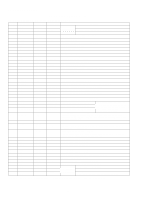

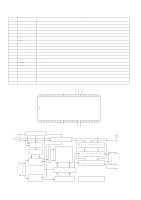

CD-XP700/CD-XP7700 IC3 VHiLC78683E-1: MP3 Decoder (LC78683E) (1/2) Pin No. Terminal Name Input/Output Function 1 LRSK 2 ADDATA 3 ADBCK 4 ADLRCK 5 C2FIN 6 TEST1 7 CKIN 8 VSS 9 CKOUT 10 TEST2 11 DVDD1 12 PW 13 SBSY 14 SFSY 15* SBCK 16 AVDD 17 VPRER 18 VCOC 19 VPDO 20 AVSS 21 DVDD2 22 VSS 23 MDATA0 24 MDATA1 25 MDATA2 26 MDATA3 27 MDATA4 28 MDATA5 29 MDATA6 30 MDATA7 31 DVDD3 32 VSS 33 MDATA8 34 MDATA9 35 MDATA10 36 MDATA11 37 MDATA12 38 MDATA13 39 MDATA14 40 MDATA15 41 RASB 42 WEB 43 CASLB 44 CASUB 45 OEB 46* MADRS12 47* MADRS11 48* MADRS10 49* MADRS9 50 MADRS8 Input Output Output Output Input Input Input - Output Input Input Input Input Input Output Input - Input Output - Input - Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input - Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Output Output Output Output Output Output Output Output Output Output CD L/R clock input. Audio data output. Audio bit clock output. Audio L/R clock output. CD C2 error flag input. Test input 1. (Must be connected to GND.) System clock (16.9344 MHz) input. GND ground pin. External DF/DAC clock (384Fs) output. Test input 2. (Must be connected to GND.) I/O digital supply pin. CD subcode data serial input. CD subcode block synchronization signal input. CD subcode frame synchronization signal input. CD subcode transfer serial clock output. Analog (PLL) supply. VCO oscillator range set pin. VCO control voltage input. VCO charge pump output. Analog GND ground pin. Internal logic supply pin. GND ground pin. DRAM data bus 0. DRAM data bus 1. DRAM data bus 2. DRAM data bus 3. DRAM data bus 4. DRAM data bus 5. DRAM data bus 6. DRAM data bus 7. I/O digital supply pin. GND ground pin. DRAM data bus 8. DRAM data bus 9. DRAM data bus 10. DRAM data bus 11. DRAM data bus 12. DRAM data bus 13. DRAM data bus 14. DRAM data bus 15. RAS output. (L-active) WE output. (L-active) CAS output. (Lower Byte, L-active) CAS output. (Upper Byte, L-active) OE output (L-active) DRAM address output 12. DRAM address output 11. DRAM address output 10. DRAM address output 9. DRAM address output 8. In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside. - 49 -